安全

网络安全

捐赠管理系统

阿克曼

libbinder

笔试题

终端

渲染

simulink

论文写作

共阴极-共阳极判定

数字图像处理

openresty

恒电势

前端3d物理引擎

osg

前端酒店管理系统

字符打印流

Cookie

完数

ic

2024/4/11 19:45:59仲裁器设计(2)RR轮询调度

上一篇固定优先级仲裁器Fixed Priority Arbiter

仲裁器设计(1)固定优先级仲裁器

里面提到了,固定优先级仲裁的一个问题就是公平性。以上篇文章里同学举手老师点名的例子来说,如果老师每次都叫学号小的,那学号大的同学…

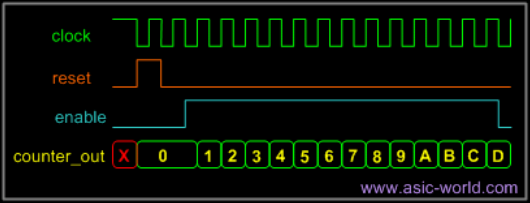

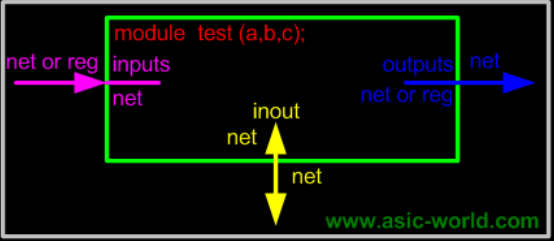

ASIC-WORLD Verilog(6)运算符

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----asic-world网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。 这是网站原文&…

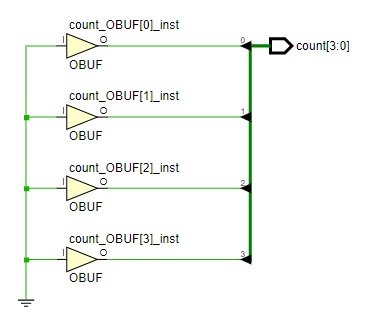

【FPGA/IC】RAM-Based Shift Register Xilinx IP核的使用

前言

一般来讲,如果要实现移位寄存器的话,通常都是写RTL用reg来构造,比如1bit变量移位一个时钟周期就用1个reg,也就是一个寄存器FF资源,而移位16个时钟周期就需要16个FF,这种方法无疑非常浪费资源。

Xili…

从零开始入门芯片行业

为中华芯片事业发展而奋斗! ——鲁迅 目录

一、设计、验证怎么选?

二、怎么学习?

2.1 IC验证

2.2 FPGA

2.3 IC设计 一、设计、验证怎么选?

非科班出身的童鞋,转行建议首选IC验证。为什么?

由于验证…

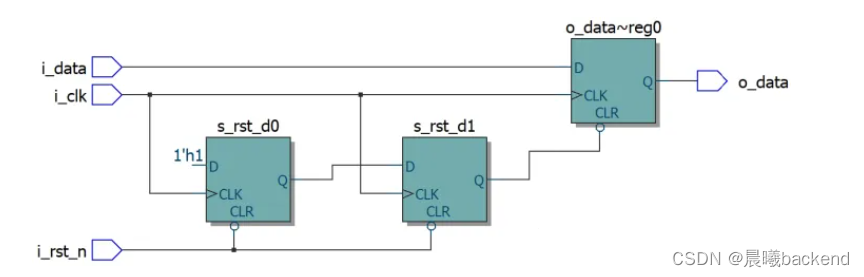

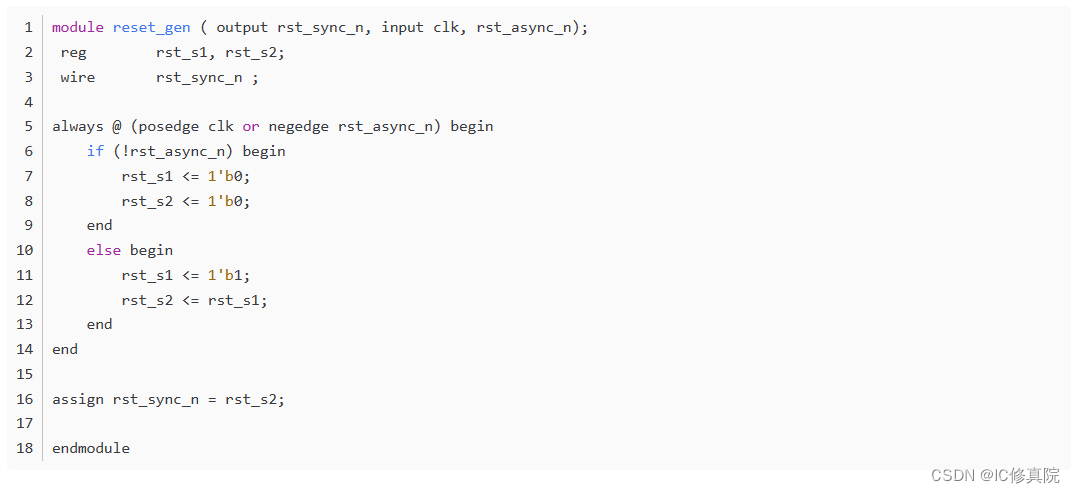

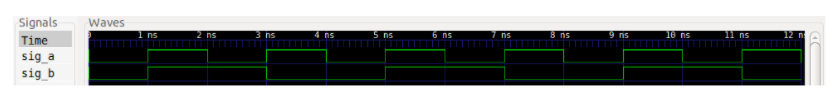

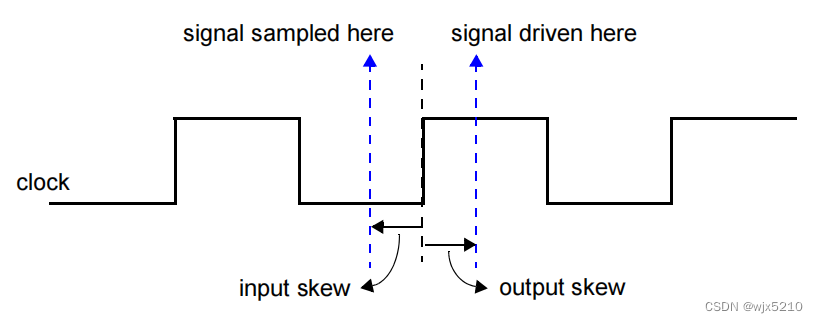

同步和异步、同步复位、异步复位、同步释放(Verilog、Verdi、DC综合)

文章目录 1.同步和异步2. 同步复位、异步复位、同步释放2.1 同步复位2.1.1 Verilog code2.1.2 Verdi waveform2.1.3 DC Synthesis 2.2 异步复位2.2.1 Verilog code 2.3 同步释放(异步信号和CLK信号存在时序检查、Recover time&Removel time)2.4 异步…

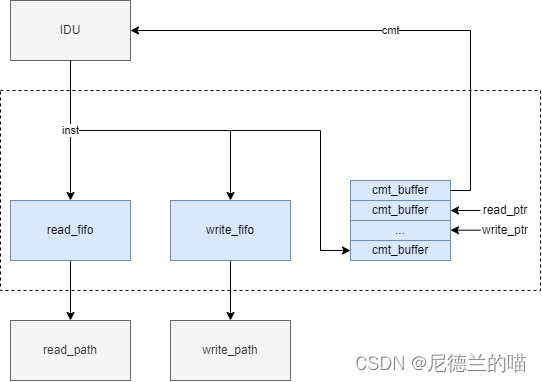

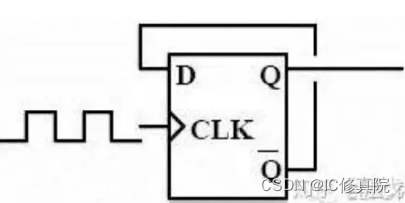

【IC前端虚拟项目】inst_buffer子模块DS与RTL编码

【IC前端虚拟项目】数据搬运指令处理模块前端实现虚拟项目说明-CSDN博客 需要说明一下的是,在我所提供的文档体系里,并没有模块的DS文档哈,因为实际项目里我也不怎么写DS毕竟不是每个公司都和HISI一样对文档要求这么严格的。不过作为一个培训的虚拟项目,还是建议在时间充裕…

【IC前端虚拟项目】MVU FS文档编写与注意事项

【IC前端虚拟项目】数据搬运指令处理模块前端实现虚拟项目说明-CSDN博客 FS文档即模块特性说明文档:

FS - Functional Specification(功能规格):"FS" 表示功能规格,它是芯片设计和开发的早期阶段的一个文档。功能规格详细描述了芯片的功能、性能和特性,以及各…

资深IC工程师的快速学习指南《Verilog语言知识学习快速基础学习》

Verilog语言是一种硬件描述语言(HDL),广泛用于数字集成电路(IC)设计和硬件描述。对于IC行业的初学者来说,掌握Verilog语言是非常重要的,因为它是设计和仿真IC电路的基础。之前也分享过很多Veril…

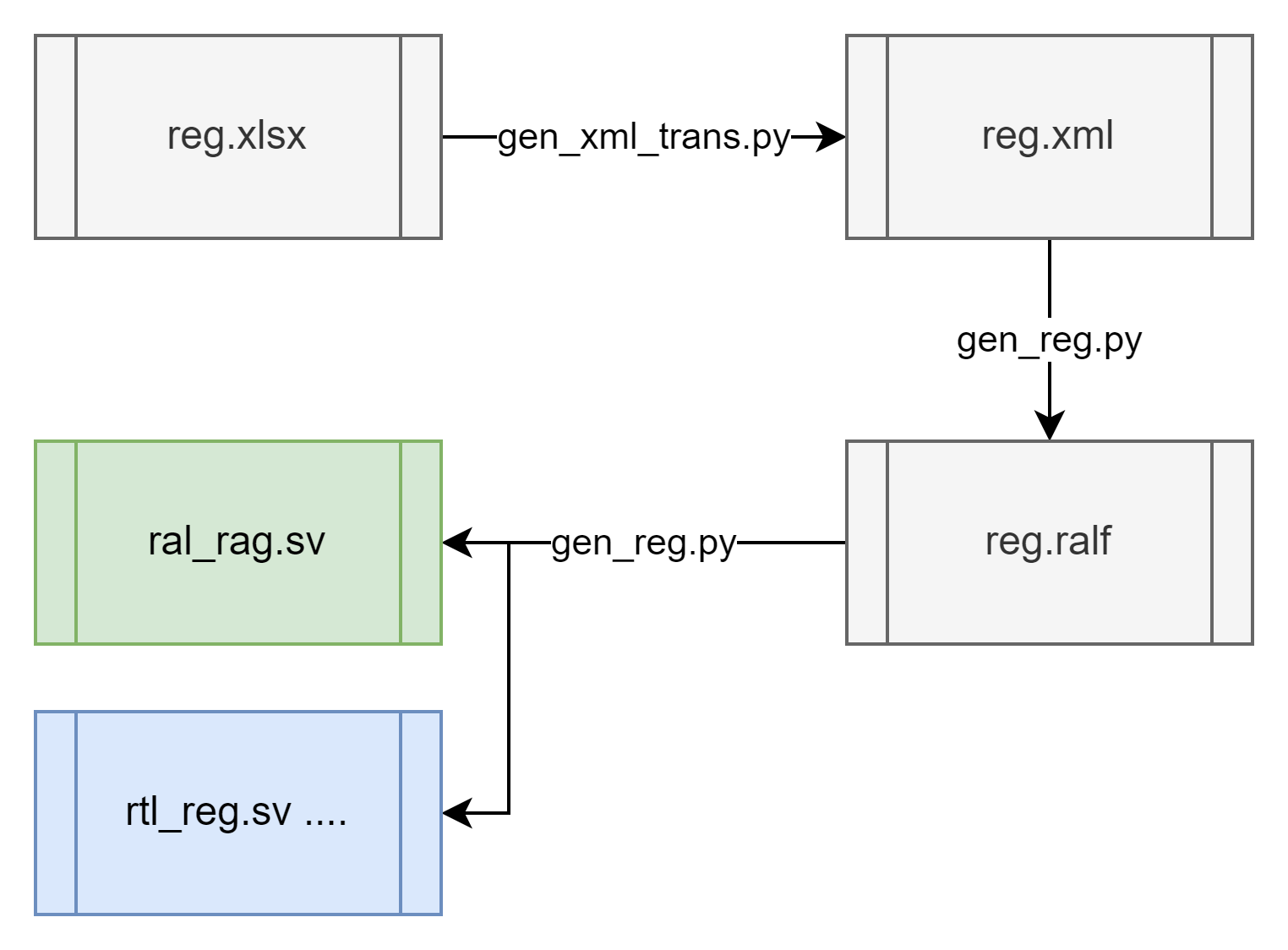

【芯片验证】通关寄存器与ral_model —— 寄存器生成流程中加入backdoor后门配置

前言

【芯片验证】通关寄存器与ral_model —— backdoor后门访问实操测试-CSDN博客

上一篇文章中,我们通过在环境中配置后门路径的方式来实现了寄存器的后门访问,但是在实际应用中,无论寄存器RTL文件、例化还是寄存器模型大概率都是工具生成的,比如在本专栏中实现的gen_r…

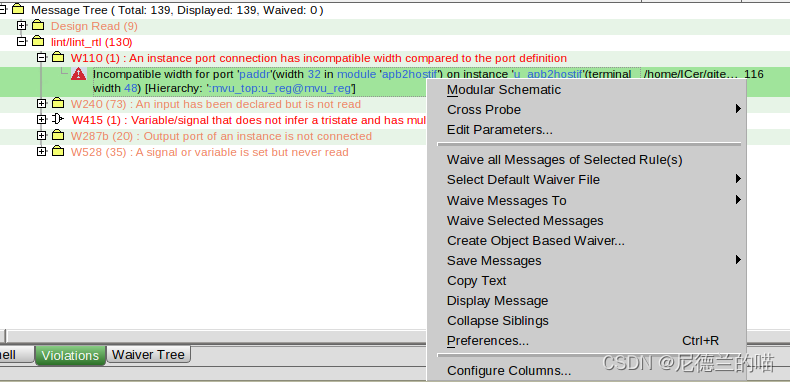

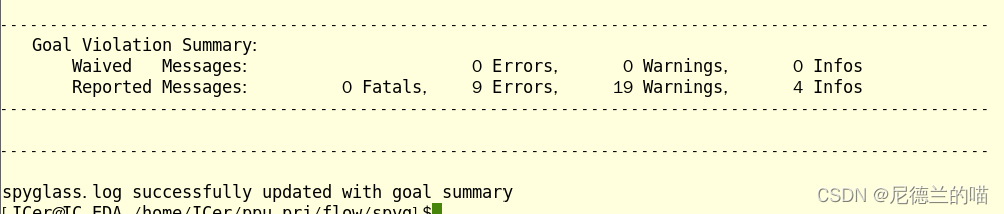

【IC前端虚拟项目】spyglass lint环境组织与lint清理

【IC前端虚拟项目】数据搬运指令处理模块前端实现虚拟项目说明-CSDN博客 和上个虚拟项目的lint清理环节一样,关于spyglass的lint清理功能与流程还是大家通过各种资料去学习下就好啦。和之前不同的事,这次的虚拟项目里我把流程封装为Makefile,…

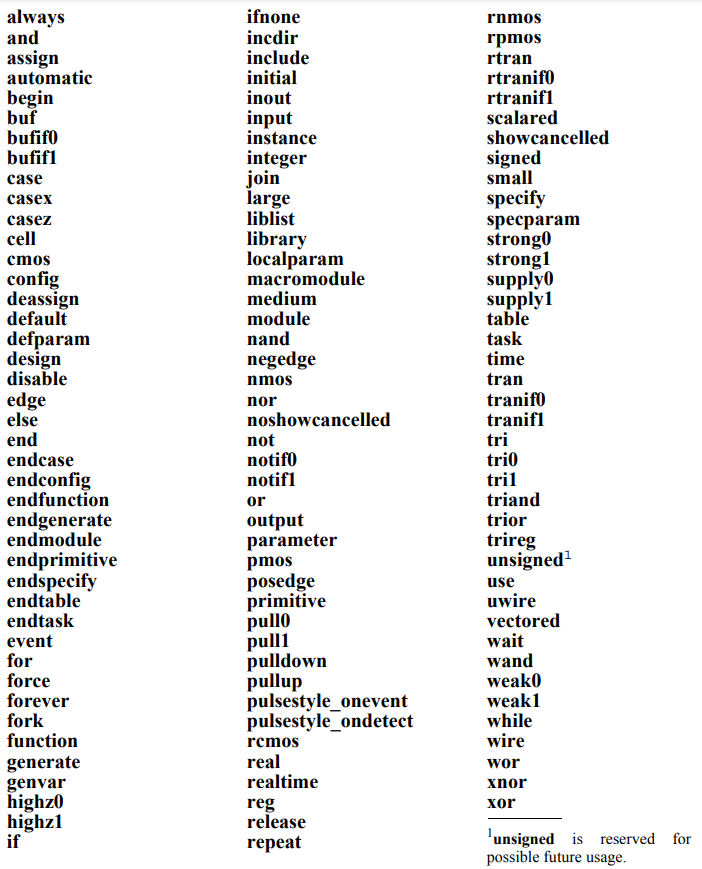

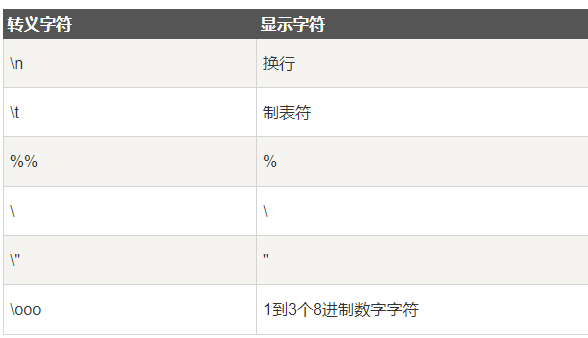

深入浅出学Verilog--基础语法

1、简介 Verilog的语法和C语言非常类似,相对来说还是非常好学的。和C语言一样,Verilog语句也是由一连串的令牌(Token)组成。1个令牌必须由1个或1个以上的字符(character)组成,令牌可以是&#x…

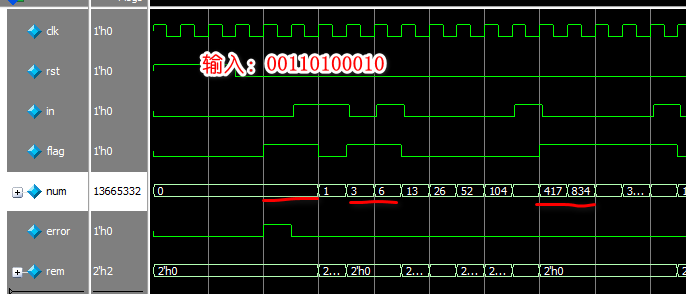

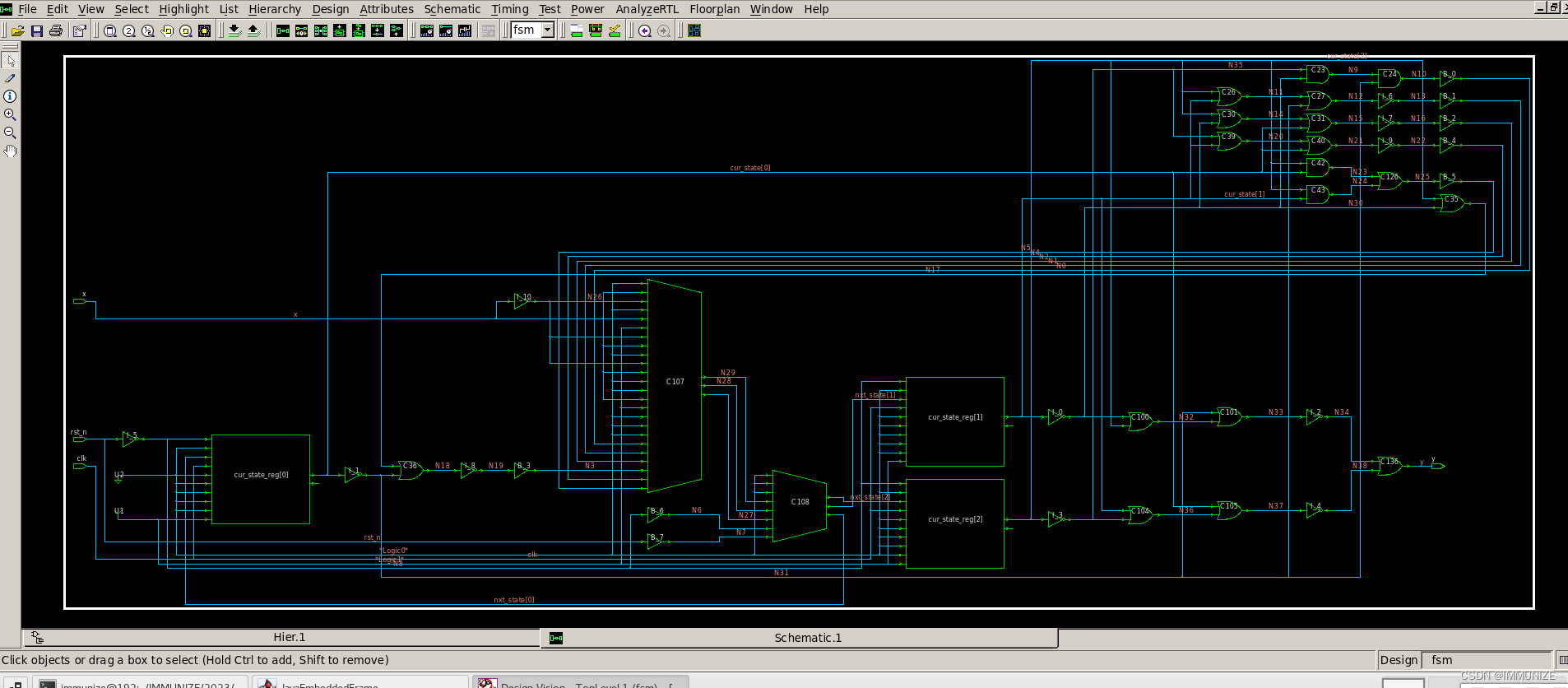

【数字IC/FPGA】手撕代码:模3检测器(判断输入序列能否被3整除)

今天我们来手撕一个常见的笔试题:模3检测,使用的方法是三段式Moore状态机。

题目描述: 输入端口是串行的1bit数据,每个时钟周期进来一位新数据后,实时检查当前序列是否能整除3,若能则输出1,否则…

入行IC | 新人入行IC选择哪个岗位更好?

很多同学入行不知道怎么选择岗位。IC的岗位一般有设计、验证、后端、封装、测试、FPGA等等。但是具体到每个人身上,就要在开始的时候确定下你要找的职位,可以有两个或三个,但是要分出主次,主次不分会让你纠结整个找工作的过程。

…

数字 IC 设计职位经典笔/面试题(三)

共100道经典笔试、面试题目(文末可全领) 1. IC 设计中同步复位与异步复位的区别?

同步复位在时钟沿变化时,完成复位动作。异步复位不管时钟,只要复位信号满足条件,就完成复位动作。异步复位对复位信号要求…

ATE测试工程师的薪资前景如何?能转DFT工程师吗?

在芯片行业,ATE测试工程师扮演着至关重要的角色。他们不仅需要理解电路和芯片内部的工作原理,还需要利用各种测试工具和方法对芯片进行精确的测试和分析。那么ATE测试工程师前景如何?需要具备哪些技能要求呢?

首先来了解什么是AT…

建议收藏《2023华为海思实习笔试-数字芯片真题+解析》(附下载)

华为海思一直以来是从业者想要进入的热门公司。但是岗位就那么多,在面试的时候,很多同学因为准备不充分,与岗位失之交臂,无缘进入该公司。今天为大家带来《2023华为海思实习笔试-数字芯片真题解析》题目来源于众多网友对笔试的记录…

解读AXI协议,做一个不被AXI折磨的芯片设计工程师

作为一名IC芯片工程师,我深知AXI(Advanced eXtensible Interface)协议给我们带来的痛苦和挑战。在过去的项目中,我经历了与AXI协议相关的许多问题和困惑,但我也学到了一些宝贵的经验。现在,我想分享一些关于…

初入行的IC工程师,如何快速提高自己的竞争力?

要想成为越来越吃香的IC工程师,就会先经历初期的成长阶段。今天就来聊聊初入行的ICer如何快速提升自己的竞争力(验证篇)。

首先希望大家在选择IC行业的时候就有清晰的认知,这是一个不得不深耕技术的行业。我们今天所谈论的快速提…

芯片后端的APR是指什么?

APR,代表自动布局与布线(Auto Placement & Route),已经成为芯片后端设计的重要部分。在当今EDA(电子设计自动化)工具高度发展的背景下,手动摆放单元格并绘制连线已经变得不切实际。因此&…

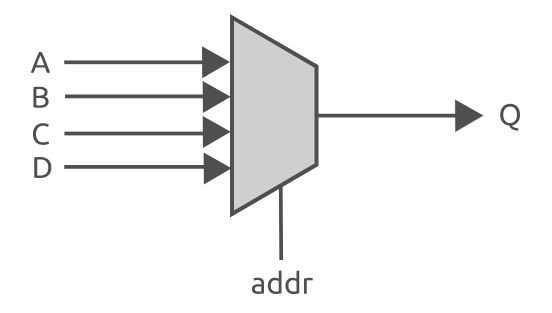

【FPGA】正确处理设计优先级--或许能帮你节省50%的资源

概述

假如现在有一种方法–可以在不怎么需要修改已有设计的情况下,就可以帮您节省50%的设计资源,那你会试试看吗?

当前市场环境下,更低廉的成本却可获得同等性能无疑是极具诱惑的。本文将介绍一种FPGA设计技术,该技术…

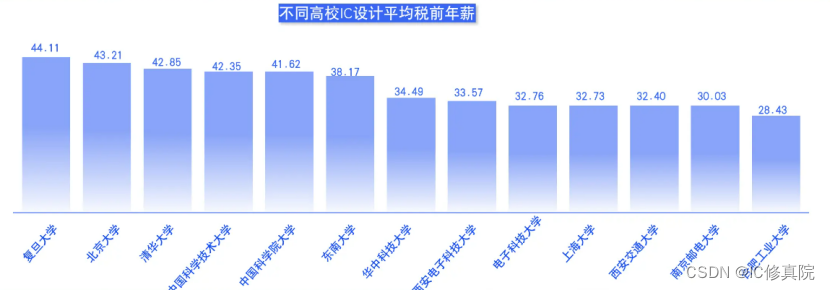

想考研到电子类,未来从事芯片设计,目前该怎么准备?

最近看不少天坑学子想考研微电子专业,但却不知道该怎么准备?接下来就带大家一起来具体了解一下~

首先是目标院校的选择?

目前所设的微电子专业学校里,比较厉害的有北京大学、清华大学、中国科学院大学、复旦大学、上海交通大学、…

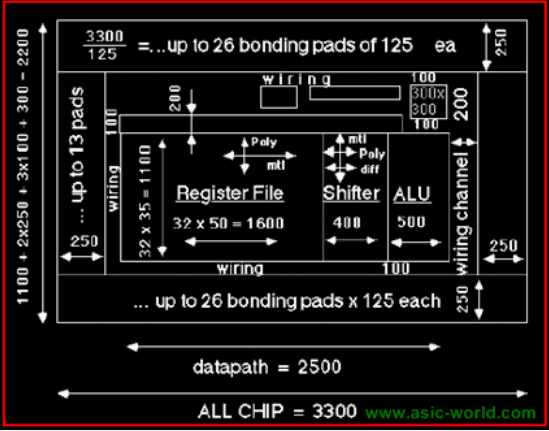

ASIC-WORLD Verilog(16)综合

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----Asic-World网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加点自己的理解)分享给大家。 这是网站原文&…

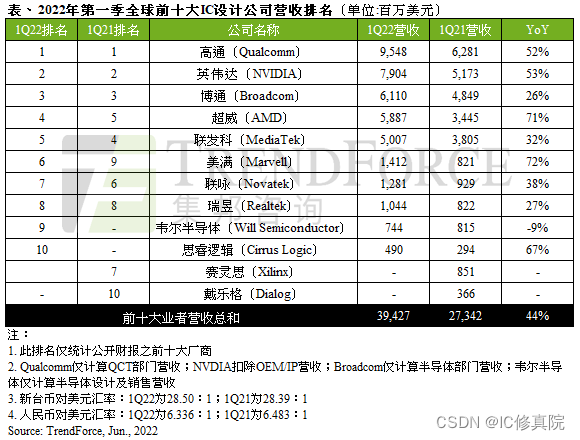

2022年全球十大IC设计公司最新排名出炉

前不久,TrendForce(集邦咨询)发布了2022年Q2全球IC设计公司的营收排名。

2022年Q2全球前十大IC设计业者营收395.6亿美元(约合人民币2874亿),年增长率32%。

先说说与上一季度(2022年Q1…

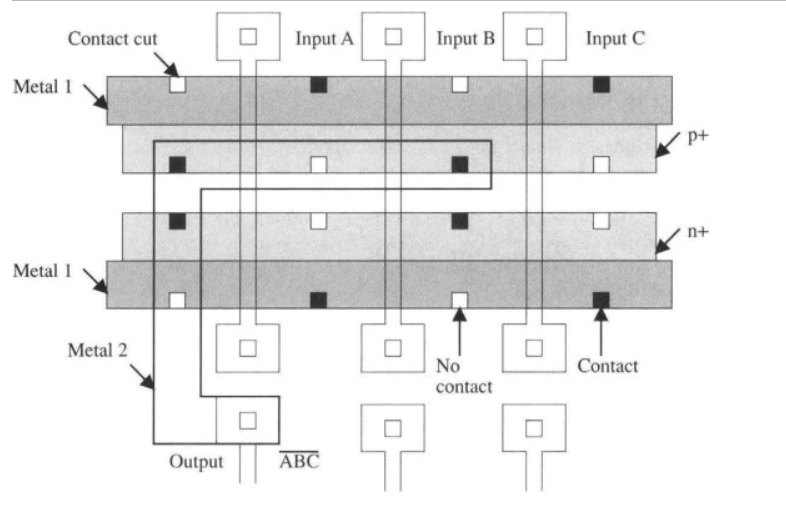

VLSI 半定制设计方法 与 全定制设计方法【VLSI】

VLSI 半定制设计方法 与 全定制设计方法【VLSI】VLSI 半定制设计方法1. standard cell 设计方法Standard Cell library设计方法与步骤特点2. 门阵列(gate array)设计方法gate array特点与FPGA的区别PLA3. 门海设计方法(sea-of-gates styles)全定制:无约束设计方法&a…

【HISI IC萌新虚拟项目】ppu模块基于spyglass的lint清理环境搭建与lint清理

关于整个虚拟项目,请参考: 【HISI IC萌新虚拟项目】Package Process Unit项目全流程目录_尼德兰的喵的博客-CSDN博客 前言

RTL代码在交付给验证同时进行功能验证时,可以同步进行lint的清理工作。一般而言影响编译和仿真的问题会在vcs的error和warning中被修正,因此清理lin…

芯片嵌入式是否如传说中那么简单?

智能化、数字化、信息化是时代大潮流。

所谓智能化,其实就是在电子产品或设备中嵌入“计算机”,来实现人机交互、采集传感器数据、处理数据、通信等功能。

而嵌入式正是连接硬件和软件的关键因素。

这里放个口:芯片嵌入式了解

芯片嵌入式…

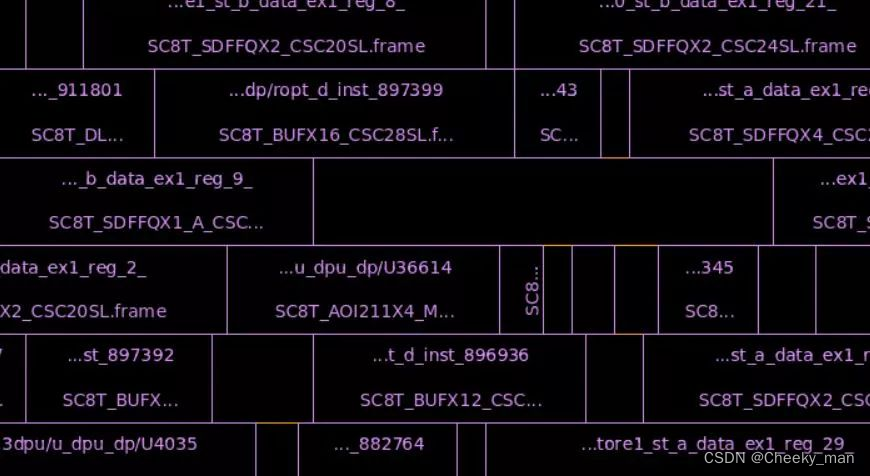

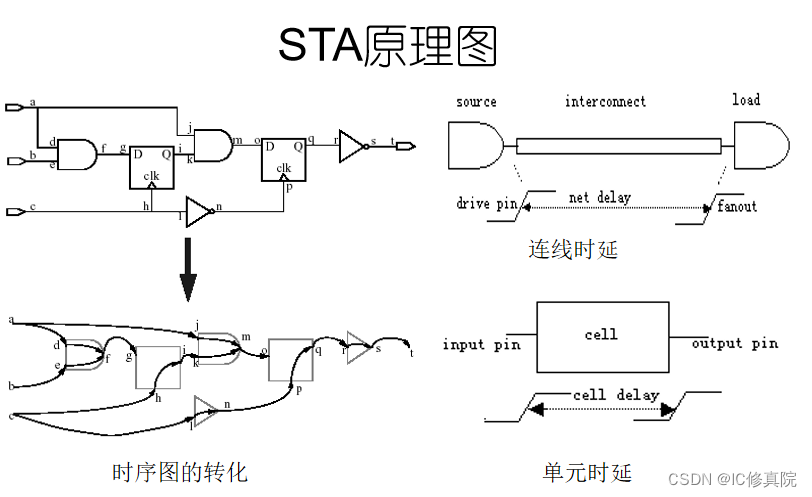

【IC萌新虚拟项目】spt_core模块基于dc的综合环境搭建与面积时序优化

关于整个虚拟项目,请参考: 【IC萌新虚拟项目】Package Process Unit项目全流程目录_尼德兰的喵的博客-CSDN博客 前言

当验证的同学正在疯狂写测试点,补充测试用例各种找茬找bug时候,设计的同学也要进入到跑综合修时序优化面积的阶段了。

还是老样子,关于芯片综合的知识就…

ASIC-WORLD Verilog(8)if-else语句和case语句

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----Asic-World网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。 这是网站原文&…

一卡通水控电控开发踩过的坑

最近在做一个项目,是对接一卡通设备的。我一开始只拿到设备和3个文档开局。不知道从哪下手。一步一步踩坑过来。踩了很多没有必要的坑,写出来给有用的人吧。

读卡器怎么用?

有个读卡器,一开始什么软件也不提供。我都不知道是干嘛…

ASIC-WORLD Verilog(2)FPGA的设计流程

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----asic-world网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。 这是网站原文&…

Verilog Tutorial(7)If语句和Case语句

写在前面在自己准备写verilog教程之前,参考了许多资料----FPGA Tutorial网站的这套verilog教程即是其一。这套教程写得不错,只是没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。这是网站原文:h…

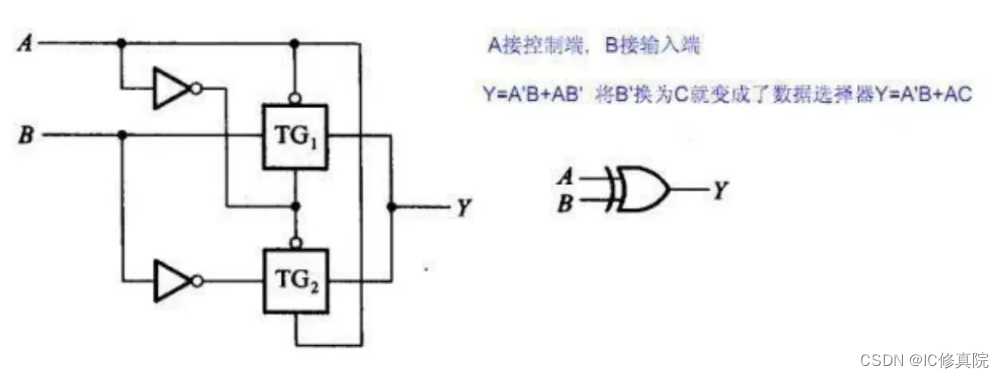

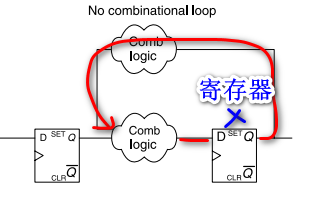

<FPGA>好的编码风格(1)--尽量避免组合逻辑环路(Combinational Loops)

什么是组合逻辑环路? 组合逻辑环路(Combinational Loops):指组合逻辑的输出信号不经过任何时序逻辑(FF等),而是直接反馈到输入节点,从而构成的电路环路。 此外,如果直接将…

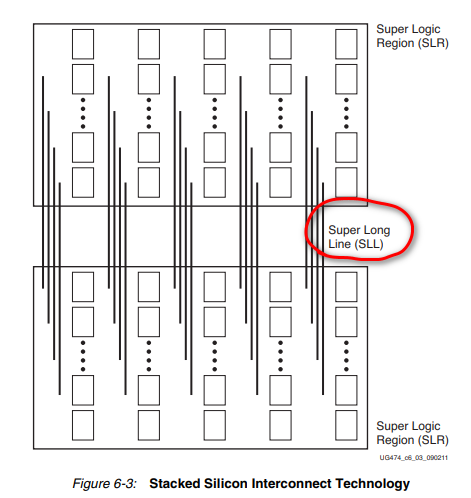

从底层结构开始学习FPGA(0)----FPGA的硬件架构层次(BEL Site Tile FSR SLR Device)

系列目录与传送门

《从底层结构开始学习FPGA》目录与传送门 Xilinx的FPGA,从硬件架构的角度可以划分为6个层次,从底层到顶层依次是:

BEL(最底层单元)SiteTileFSRSLRDevice(FPGA芯片) 接下来我…

HDLBits-Verilog学习记录 | Verilog Language-Basics(1)

文章目录 3.Simple wire4.Four wires5.inverter | Notgate6. And gate7.Nor gate8.Xnorgate 3.Simple wire

problem:Create a module with one input and one output that behaves like a wire.

module top_module( input in, output out );assign out in;endmodule4.Four w…

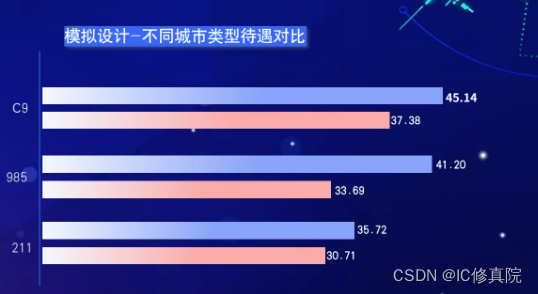

2023年模拟IC就业形式怎么样? 还能不能入了?(附最新薪资行情)

虽然说模拟IC的门槛高,难度大,但相比数字IC的话竞争要小一点。而且薪资也比数字IC要高一些。

想要学好模拟芯片设计,首先要懂电路,懂器件,你要理解你的器件是怎么工作的,它在芯片上是什么样子,…

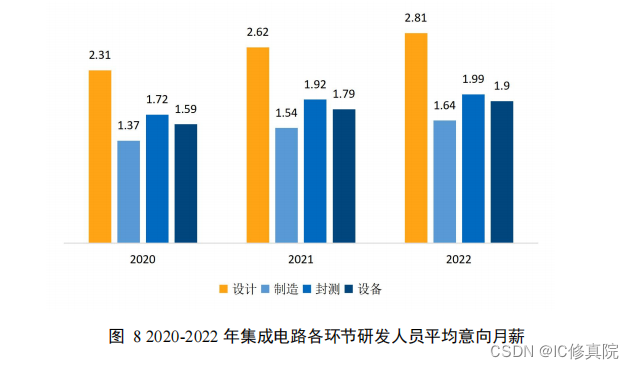

入行IC | 从小白助理级,到总监专家级,到底要经历怎样的成长阶段呢?

《中国集成电路产业人才发展报告》是业内和IC设计、IC人才都息息相关的一份报告。

(文末可领全部报告资料)

*

从报告数据来看,无论在半导体产业的哪个环节,个人发展路径和年薪待遇都是逐级攀升的趋势。

那么从小白助理级&a…

quartus+modelsim仿真教程

一、编写设计程序 1、新建工程: 打开quartus软件,菜单栏:File->New Project Wizard,然后得到下图界面:点击next。 在该界面中需设置工程目录以及工程名。 本项目没有写好的代码,直接点击next进入下一步…

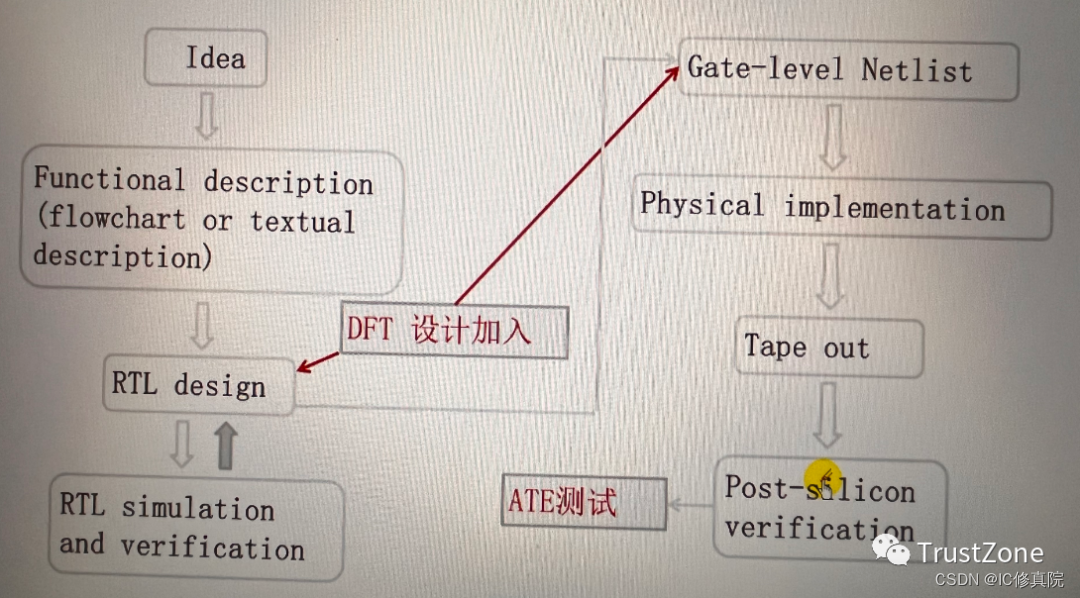

IC流程中 DFT 学习笔记(2)

引言

DFT是ASIC芯片设计流程中不可或缺的环节。其主要目的是在芯片前端设计验证完成后插入一些诸如寄存器链等可供测试的逻辑,算是IC后端设计的范畴,属于结构测试而非功能测试。主要是在ASIC芯片流片完成后,通过这些已插入的逻辑,…

你觉得哪个软件写verilog体验最好?

最近在媒体上看到一个热点问题,浏览量高达680,003。“你觉得哪个软件写verilog体验最好?”这个问题可以说是IC设计师们最想知道的问题,也是大家工作交流中比较常见的。今天移知教育小编就来为大家分享一下,我对于这个问题的解答。…

数字IC验证高频面试问题整理—附答案(三)

最近大家无不在讨论IC秋招,秋招想必缺的就是面试题目了。这不就来了~

共150道验证高频面试题整理~含答案(文末可领取全部题目)

Q1.二进制码、格雷码、独热码的特点

二进制码:基本的机器语言,每一位只能是0或1&…

提高工作效率,《Linux常用命令文件配置》

在IC设计领域,所有的开发任务几乎都是在Linux操作系统上完成,因此需要掌握Linux操作系统的使用;Linux可以为工程师提供更好的开发环境和调试工具。还支持多种开发语言和编程环境,可以为数字IC芯片工程师提供更多的选择和灵活性。

作为IC工程…

ASIC-WORLD Verilog(15)存储单元

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----Asic-World网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加点自己的理解)分享给大家。 这是网站原文&…

IC工程师的护城河是什么?看过来人总结

某个做安卓开发的大佬分享自己的经历:

当初安卓刚兴起的时候,会做一个安卓APP一定是稀有的人才,因为当时能掌握安卓开发技术的人很少。

而现在如果只会开发安卓APP的话,大概率很难找到工作,你需要掌握更多的知识&…

IC行业秋招真实情况记录,快来看看吧~

2023年,IC行业人才竞争尤为激烈。为了更好的获取到面试的经验,不妨先来了解一下IC面试常见的问题,以及面试该准备的相关事项吧~

(文末可领全部面试题目)

什么是同步逻辑和异步逻辑?

同步逻辑是时钟之间…

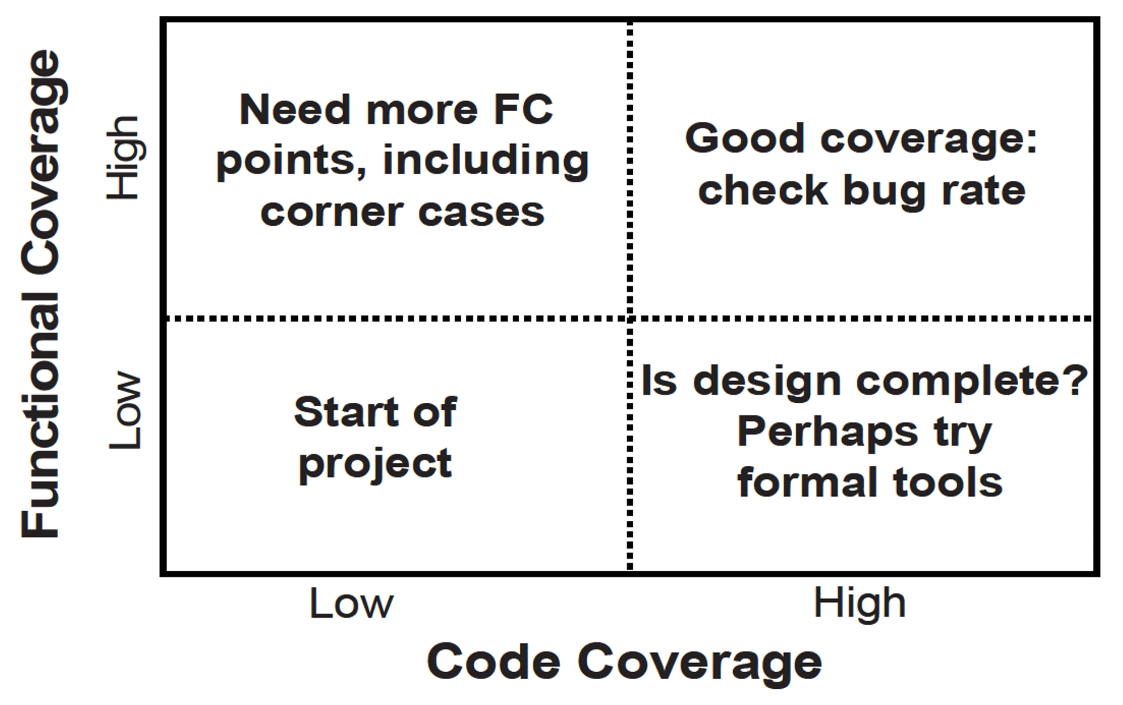

数字IC芯片验证流程及验证工具推荐?收藏专用

验证其实是一个“证伪”的过程,从流程到工具,验证工程师的终极目的都只有一个:

发现所有BUG,或者证明没有BUG,以保证芯片功能性能的正确性和可靠性。

验证环节对于一颗芯片的重要性也是不言而喻的:

从项…

ATE测试工程师的前景待遇如何?薪资天花板有多高?

在芯片行业,ATE测试工程师扮演着至关重要的角色。

他们不仅需要理解电路和芯片内部的工作原理,还需要利用各种测试工具和方法对芯片进行精确的测试和分析。那么ATE测试工程师前景如何?需要具备哪些技能要求呢?

首先来了解什么是…

Verilog实现2进制码与BCD码的互相转换

1、什么是BCD码?

BCD码是一种2进制的数字编码形式,用4位2进制数来表示1位10进制中的0~9这10个数。这种编码技术,最常用于会计系统的设计里,因为会计制度经常需要对很长的数字做准确的计算。相对于一般的浮点式记数法,…

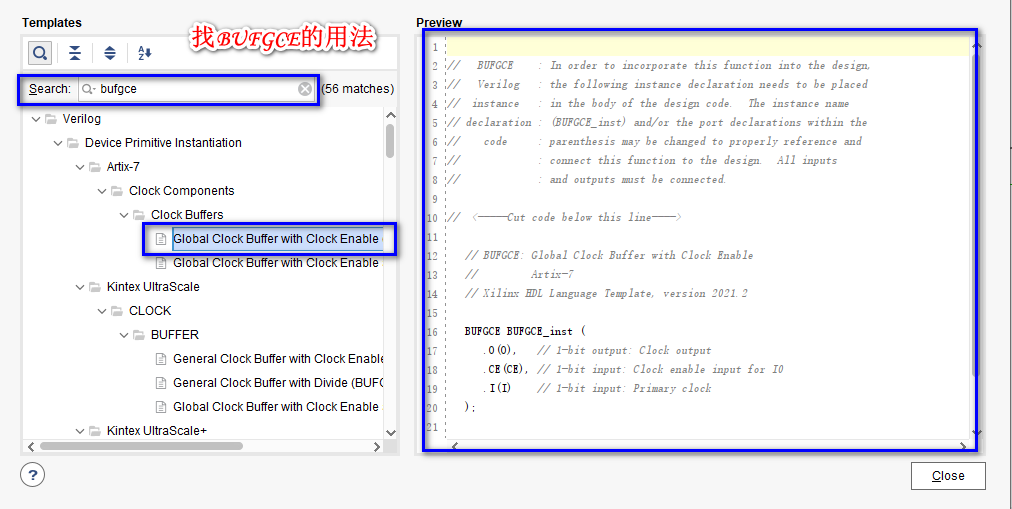

好的FPGA编码风格(2)--多参考设计软件的语言模板(Language Templates)

什么是语言模板? 不论是Xilinx的Vivado,还是Altera的Quartus II,都为开发者提供了一系列Verilog、SystemVerilog、VHDL、TCL、原语、XDC约束等相关的语言模板(Language Templates)。 在Vivado软件中,按顺序…

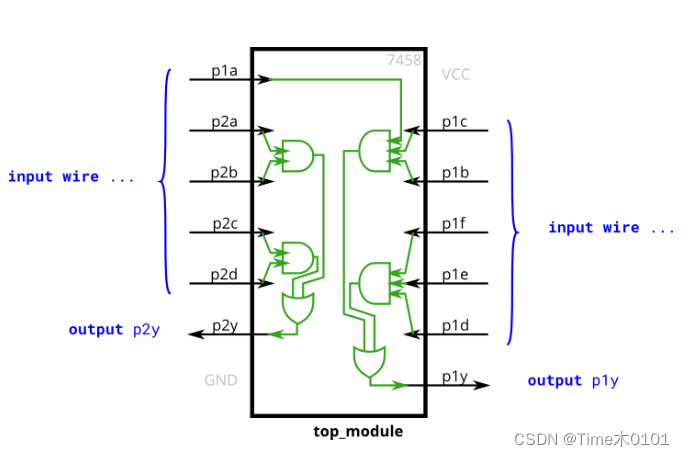

HDLBits-Verilog学习记录 | Verilog Language-Basics(2)

文章目录 9.Declaring wires | wire decl10. 7458 chip 9.Declaring wires | wire decl

problem:Implement the following circuit. Create two intermediate wires (named anything you want) to connect the AND and OR gates together. Note that the wire that feeds the …

IC工程师职场必备《经典Verilog100多个代码案例》(附下载)

对于IC行业的人员而言,Verilog是最基础的入门,用于数字电路的系统设计,很多的岗位都会用到,可对算法级、门级、开关级等多种抽象设计层次进行建模。

Verilog由于其简单的语法,和C语言的相似性,目前被各大公…

为什么很多人从FPGA转IC前端岗?哪个前景好?

很多入行不久的朋友潜意识里会认为FPGA是很高深的东西,能掌握FPGA的一定都是极其厉害的人。

其实,这是一个误解。

我们所讨论的FPGA只是基于已有的FPGA芯片去做后端排列组合的工作内容,而不是设计制造新的FPGA芯片,世界上能做这…

IC设计的前端和后端是如何区分的?

一、工作着重点不同

**1、IC前端:**根据芯片规格书完成SOC的设计和集成, 使用仿真验证工具完成SOC的设计验证。

**2、IC后端:**将前端设计产生的门级网表通过EDA设计工具进行布局布线和进行物理验证并最终产生供制造用的GDSII数据

二、工作…

IC设计职位介绍|如何成为一名合格的数字前端设计工程师?

近年来IC行业火热,但因为一些原因,今年以来行业唱衰的人越来越多。尽管全球芯片市场过剩,但我国的半导体行业发展很可观,目前政策倾向国产芯片的发展,所以半导体人才非常稀缺。我国半导体产业终究要崛起,因…

GPU是什么?GPU有多重要?

前段时间,MD和英伟达相继接到通知要对我国断供高端GPU芯片,很多人不知道GPU到底有什么用?下面IC修真院就带大家来一起了解一下GPU。

首先来了解一下GPU是什么?

GPU–图形处理器(Graphics Processing Unit)…

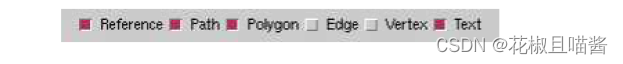

Calibre DESIGNrev Object Selection Toolbar

包括 Reference Path Polygon Edge Vertex Text的解释说明

FieldDescription用法(勾选后)ReferenceUsed to move or select a cell reference or array reference.可以选择一个cellPathUsed to move or select a contiguous path object.暂时不明请指教…

IC验证之SDIO使用

IC验证之SDIO使用SD控制器和SDIO卡初始化流程如下:1. 配置SD控制器的寄存器:1) 配置控制寄存器CTRL,bit0置高复位控制器,bit1置高复位FIFO,bit2置高复位DMA,bit4置高使能中断,bit5置…

AMBA_AXI Protocol Introduction

AXI Protocol Introduction

1. AXI协议特性

2. AXI协议关键特性

3. AXI 协议结构

4. Interface and interconnect

5. Register slicesAMBA AXI协议为主机与从机组件之间的通信提供高性能,高频系统设计 1. AXI协议特性

适用于高带宽,低延迟设计不使用复…

Verilog Tutorial(8)循环语句

写在前面在自己准备写verilog教程之前,参考了许多资料----FPGA Tutorial网站的这套verilog教程即是其一。这套教程写得不错,只是没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。这是网站原文:h…

UVM结构篇之八大组件功能概述

UVM是一种统一的验证方法,它是至关重要的,有不少人往IC验证方向发展的,多多少少都会去了解UVM。对于验证工程师来说,掌握UVM可以大大减轻验证工程师跨公司、跨项目工作的难度。

UVM

通用验证方法学(Universal Verifi…

IC行业四大岗位详细介绍,0基础入门必读

很多人想要转行IC,但不知道该如何选择岗位,不知道这些岗位以后具体是做什么的,需要什么工作技能?其实转行选择岗位是一件大事,一定要根据自己的条件选择适合自己的岗位。

数字前端设计工程师

①读文档,写…

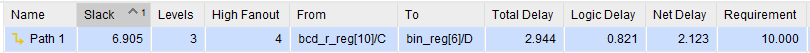

【IC前端虚拟项目】时序面积优化与综合代码出版本交付

【IC前端虚拟项目】数据搬运指令处理模块前端实现虚拟项目说明-CSDN博客 到目前为止,我们完成了第一版综合,那么就可以打开报告看一下了,一看就会发现在1GHz时钟下时序真的很差(毕竟虚拟项目里使用的工艺库还是比较旧的,如果用12nm、7mn会好很多): Timing Path Group cl…

2024届数字IC秋招-华为机试-数字芯片-笔试真题和答案(一)(含2022年和2023年)

文章目录 前言1、已知a = 1b1;b = 3b001,那么{a,{2{b}}} = ( )2、在一个SOC中数据通路中,Master到Slaver 的单命令完成Latency是100Cycle,能支持的最大命令Outstanding是10,则完成10个命令访问的最小平均Latency大约是( )3、generate语句中的循环控制变量应该定义为( )类…

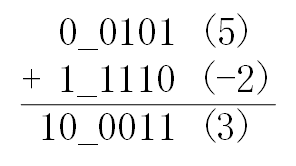

【数字IC/FPGA】什么是无符号数?什么是有符号数?

进制

虽然在日常生活中,我们已经习惯了使用10进制数字,但在由数字电路构成的数字世界中,2进制才是效率更高的选择。

10进制与2进制

10进制(decimal)计数法(一般也叫阿拉伯计数法)是在日常生活…

AMBA_AXI Protocol_Burst Address

AXI Protocol_Burst Address

Burst Address(Bus地址)

1. Burst 地址

2. Byte lane本节提供确定突发内传输的地址和字节选通(byte lane)的方法。方程使用以下变量:

Start_Address:由主机发出的起始地址。Number_Byte…

【数字IC/FPGA】书籍推荐(1)----《轻松成为设计高手--Verilog HDL实用精解》

在下这几年关于数字电路、Verilog、FPGA和IC方面的书前前后后都读了不少,发现了不少好书,也在一些废话书上浪费过时间。接下来会写一系列文章,把一部分读过的书做个测评,根据个人标准按十分制满分来打分分享给大家。 书名…

【ICer的脚本练习】脚本使用的思维培养 —— 关键词查找

系列的目录说明请见:ICer的脚本练习专栏介绍与全流程目录_尼德兰的喵的博客-CSDN博客 前言

本文仍旧以培养脚本使用的思维和常见操作为主,不过多的进行脚本编码说明。

场景

跑完仿真之后,想查一个uvm定义的关键词在源码中的位置,后者想查查一个RTL中使用的宏是在哪个文件…

IC岗位详解| 高薪模拟版图工程师需要掌握哪些技能?

IC模拟版图设计在IC行业中是门槛相对较低的一个岗位,其他岗位大都要求是科班毕业,或者是硕士以上学历,IC模拟版图设计本科生也很好入门,对于基础差的同学这是非常好的一个入门机会。

模拟版图工程师介绍

模拟版图设计工程师为专…

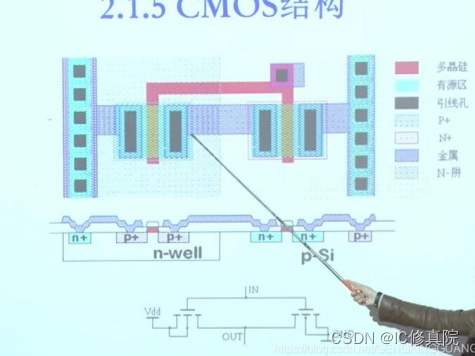

数字 IC 设计职位经典笔/面试题(四)

共100道经典笔试、面试题目(文末可全领) 画出 CMOS 电路的晶体管级电路图,实现 YA*BC(DE).?

画出 YABC 的 CMOS 电路图,画出 YABCD 的 CMOS 电路图。 利用与非门和或非门实现 YABC(DE)((AB’)(CD)’(CE)’)’ 三个两输入与非门&a…

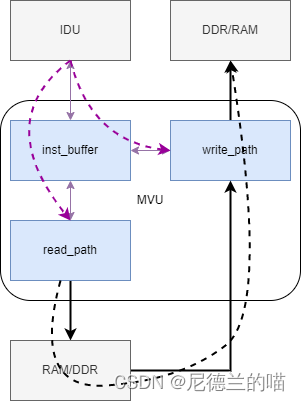

【IC前端虚拟项目】MVU模块方案与背景熟悉

【IC前端虚拟项目】数据搬运指令处理模块前端实现虚拟项目说明-CSDN博客 mvu这个模块是干嘛用的呢?从这个名字就可以看出来move_unit,应该是做数据搬运的。很多指令级中都会有数据搬运的指令,这类指令的作用一般是在片内片外缓存以及通用专用…

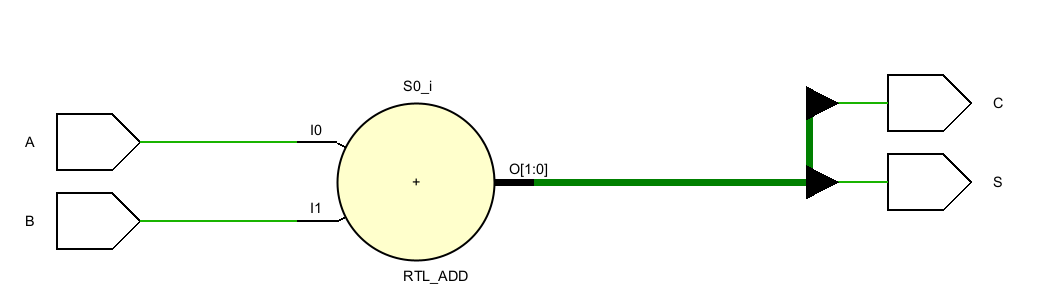

ASIC-WORLD Verilog(3)第一个Verilog代码

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----asic-world网站的Verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。 这是网站原文…

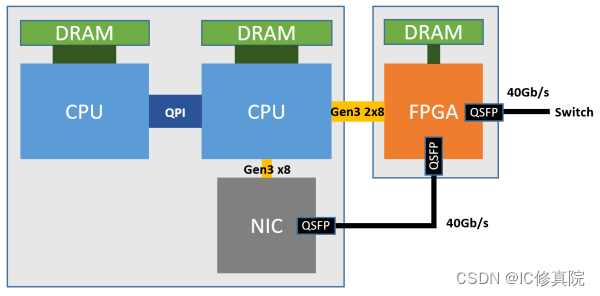

DDR与PCIe:高性能SoC的双引擎

SoC芯片无处不在,小到家电控制的MCU,大到手机芯片,我们都会接触到。如今大部分芯片设计公司都在开发SoC芯片,一颗SoC芯片可以集成越来越多的功能,俨然它已成为IC设计业界的焦点。

高性能、高速、高带宽的互联和存储的…

DFT和ATE岗位前景薪资对比,手把手教你如何选择岗位?

ATE测试和DFT可测性设计,虽然二者都对芯片测试至关重要,但是两个岗位的区别还是很大的。

两个岗位应该如何做选择? 先讲产业环节

我们知道芯片设计、芯片制造、芯片封测每个环节都是大工程,且每个环节都关键且重要。测试是芯片诞…

【FPGA】Verilog描述电路的三种方式(结构化、数据流和行为化)

前言

众所周知,Verilog是作为一种HDL(Hardware Description Language,硬件描述语言)出现的,它的主要功能是在不同的抽象层级上描述电路,从而实现电路设计。那么到底该如何描述电路?Verilog提供…

芯片行业震荡期,数字后端还可以入吗?

自去年开始,芯片行业仿佛进入了动荡期,经历了去年秋招和今年春招的小伙伴都知道,如今找工作有多难。

半导体行业人才缩减、各大厂裁员,在加上高校毕业生人数破千万,对于即将踏入IC这个行业的应届生来说,今…

材料行业可以转IC设计后端吗?

近来有许多材料行业的小伙伴通过后台来问我对于职业规划的看法,甚至有些小伙伴直接点明了某个行业适不适合自己,那么我这边仅以近年来比较热门的数字芯片设计来展开讲讲,材料适不适合转行做IC呢。

对于理工科的同学而言,选择哪个…

什么是standard cell (标准单元) ?

参考文章: 聊一聊芯片后端的标准单元-standard cell - 知乎 (zhihu.com) standard cell中的7T和9T中的"T"指的是什么?或者是什么的缩写? - Layout讨论区 - EETOP 创芯网论坛 (原名:电子顶级开发网) - 数字后端基本概念介…

【Linux/脚本/芯片学习】Perl学习

Title:Perl学习 个人学习策略 主用python. 看懂perl 和 tcl 即可。 之前的存货 开始搬砖后,整理 ”网络发布版笔记“ 的心思寡淡了好多,可能就是被工作榨干的原因8… 但今天至少得赶个1024节日… ( ̄▽ ̄)"~

1 介…

芯片设计后端遇到的各种文件类型和文件后缀

芯片设计后端遇到的各种文件类型和文件后缀 文件类型 描述 文件后缀 netlist网表文件 verilog文件格式,记录了芯片里各个instance的逻辑连接关系 .v (for Verilog netlists) Lib,liberty timing file 记录了cell的timing信息及一定power信息。有的…

模电入门必学——CMOS电路(附学习书籍,可下载)

模电就像黑魔法,没有固定的套路,要想真的学好,不断总结,不断实践才是王道。这些书就是领你进门的老师,但是以后的修行如何,就要看你勤不勤于动手了。今天为大家分享的是模电入门必学——CMOS电路࿱…

FPGA目前就业形势咋样?来听听业内工程师的看法

看到网上有一个问题很火:2023了,FPGA目前就业形势咋样?很多同学也对这个方向比较感兴趣,下面就来一起了解一下吧。

FPGA岗位有哪些?

从芯片设计流程来看,FPGA岗位可以分四类 产品开发期:FPGA系统架构师 …

Verilog基础【一】

文章目录 1.1 第一个verilog设计1.2 Verilog 简介1.3 Verilog环境搭建1.4 Verilog 设计方法设计方法设计流程 2.1 Verilog 基础语法格式注释标识符与关键字 2.2 Verilog 数值表示数值种类整数数值表示方法实数表示方法十进制:科学计数法: 字符串表示方法…

【IC前端虚拟项目】mvu顶层集成的原则与技巧

【IC前端虚拟项目】数据搬运指令处理模块前端实现虚拟项目说明-CSDN博客 截止目前,所有的子模块编码均宣告完成,接下来就是封装顶层的时刻了。我自己规划和集成顶层一般有一个习惯,就是在top层下面封装core层和其他模块,比如mvu的top层下例化了mvu_reg和mvu_core两个模块,…

HDLBits-Verilog学习记录 | Getting Started

Getting Started

problem: Build a circuit with no inputs and one output. That output should always drive 1 (or logic high).

答案不唯一,仅共参考:

module top_module( output one );// Insert your code hereassign one 1;endmodule相关解释…

【HISI IC萌新虚拟项目】test_core模块方案文档

该文档为test_core spec,仅为参考,如果在进行本系列虚拟项目的学习与实践,请自行完成本部分内容。 1.Introduction

用于对 SRAM 实现自动的可配置地址线、数据线故障检测。

1.CPU 控制

CPU 向芯片的工作模式选择寄存器写入0xXXXX_XX55后,芯片进入扫描工作模式, 并启动…

【IC前端虚拟项目】write_path子模块DS与RTL编码

【IC前端虚拟项目】数据搬运指令处理模块前端实现虚拟项目说明-CSDN博客 read_path的代码完成之后,就可以开始整个项目里复杂度最高、bug最多、时序收敛最为困难的模块——write_path的开发了!我自己写过两次这个虚拟项目,每次都是在这里耗时最久,所以大家也可以挑战一下自…

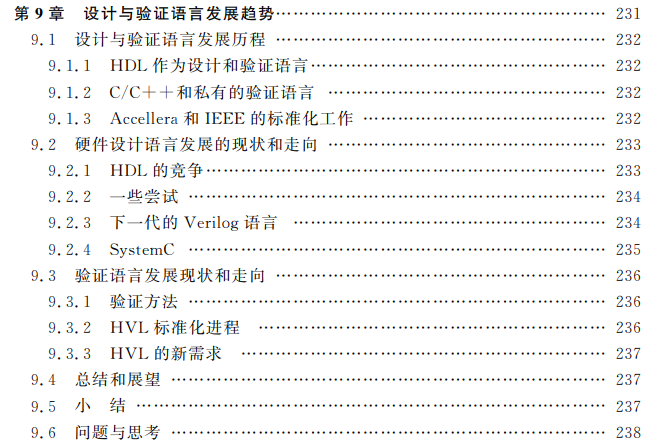

芯片设计工程师必备基本功——《设计与验证:Verilog HDL》

Verilog HDL 作为两大硬件描述语言之一,拥有很大的用户群。据调查,目前美国有 90%左右的 IC 设计人员使用 Verilog. 在中国,大概再 50% 左右的人在使用 Verilog 。

大量高校毕业生和部分软件设计人员正在不断涌入这个领域。要想尽快在 IC设计…

PCIe 5.0验证实战,经常遇到的那些问题?

PCIe 5.0是当前最新的PCI Express规范,提供了更高的数据传输速率和更大的带宽。

PCIe是连接两个芯片的接口,负责两个芯片通信, 连接芯片的通路为高速SerDes, 称之为链路。PCIe确保通路正常-链路训练状态机。PCIe在芯片内部是非常重要的一个大的模块&…

模拟IC经典面试题目及答案汇总,这些经典题目你刷到过几个?

有不少小伙伴说还想要更多模拟IC方向的面试题目,这不就来了!(文末可领全部面试题目)

请描述一下 CMOS 的工艺流程

1)光刻形成 well 阱区:在 p 型硅衬底上生长一层氧化层,涂光刻胶,…

锁向环到底是什么?是怎么进行倍频的?

你们有没有这样一个疑问,就是CPU的主频怎么做到几个GHz呢?

每一秒要给处理器几亿个脉冲,就拿11代I7处理器来说,它的基本频率就可达2.5GHz,但在我们常规的认知中,频率的大小取决于晶振的频率,比…

数字IC设计流程是怎么样的,有那些eda工具? (全流程详解)

我们通常会将数字IC的设计过程分为两个部分,分别为:前端设计和后端设计。

前端设计的主要流程:

1、规格制定 芯片规格: 芯片需要达到的具体功能和性能方面的要求

2、详细设计 就是根据规格要求,实施具体架构,划分模…

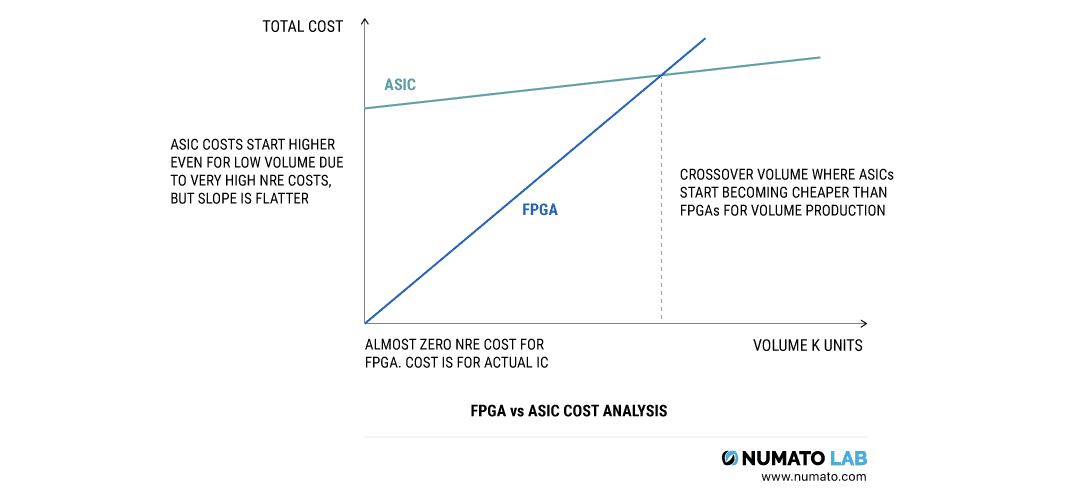

FPGA与ASIC有什么差异?二者该如何选用?

前言 对于一个数字电路的新手来说,这可能是会经常遇到的一个问题:FPGA和ASIC之间的区别是什么? 接下来本文将尝试讲解 “什么是FPGA?” 和 “什么是ASIC?”,然后讲述一些关于FPGA和ASIC的问题,例如它们之间…

ASIC-WORLD Verilog(5)基础语法下篇

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----asic-world网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。 这是网站原文&…

【HISI IC萌新虚拟项目】spt_core模块方案文档

spt_core为实现包转发功能的模块,为spt模块的核心部分。spt还包含test_core和spt_core访问sram的分发功能。该文档仅为参考 spt_core模块概述

spt_core需要实现的功能如下: 1 、根据头域 (Header) 指示,开始一包的接收;2 、净荷内容进行字节序的转换,高位字节放低位,低位…

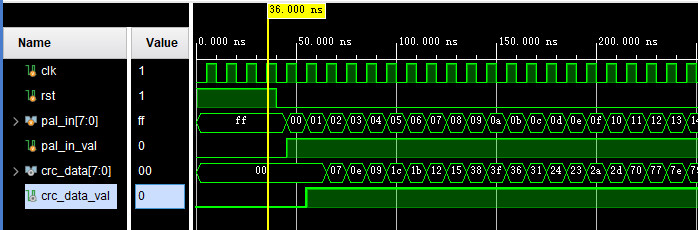

【FPGA/IC】CRC电路的Verilog实现

前言

在通信过程中由于存在各种各样的干扰因素,可能会导致发送的信息与接收的信息不一致,比如发送数据为 1010_1010,传输过程中由于某些干扰,导致接收方接收的数据却成了0110_1010。为了保证数据传输的正确性,工程师们…

行业观察 | 芯片设计产业链:上游至下游

本文简单总结、介绍芯片设计产业链全流程。

更新:2023 / 7 / 2 文章目录 集成电路产业链常见的芯片架构图数字IC设计流程概略版详解版前后端前端:RTL -> Netlist后端:Netlist -> Layout 示例:基于标准单元(STD …

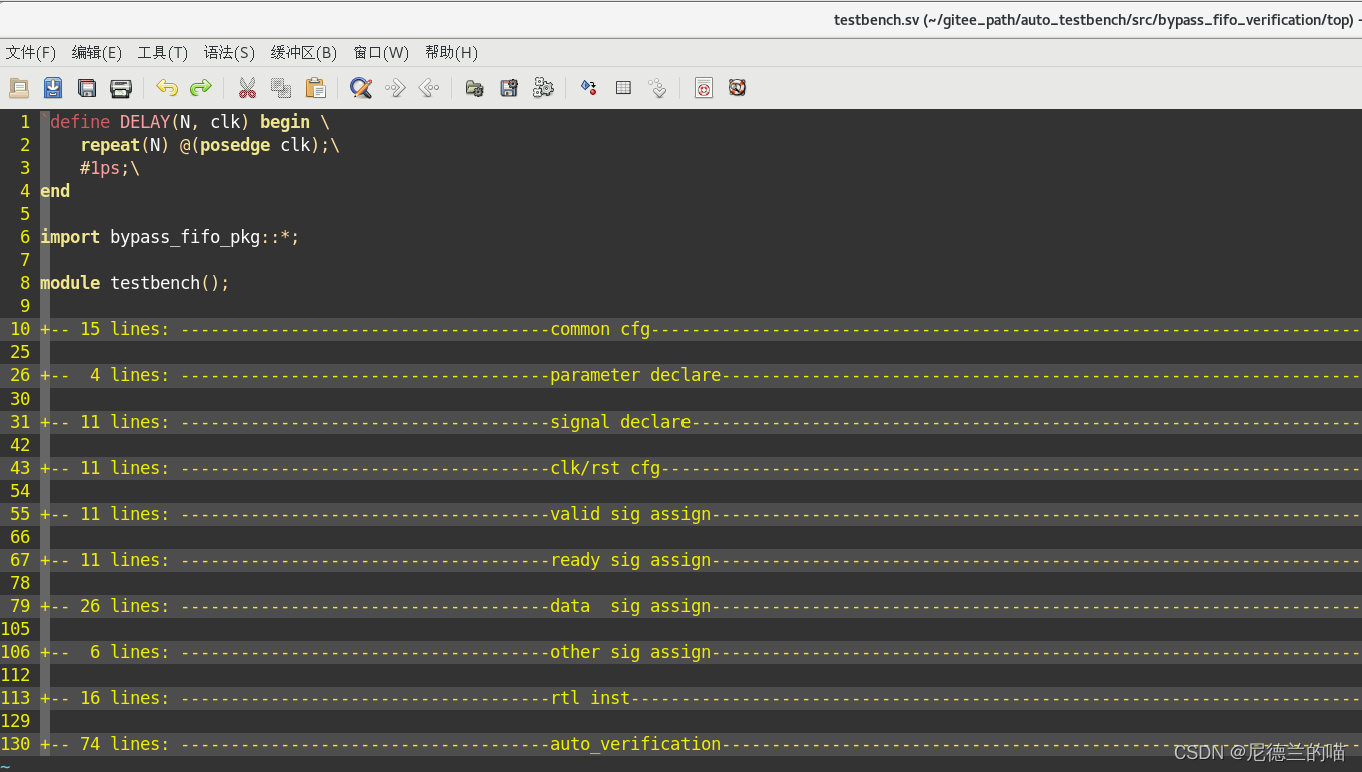

【芯片前端】auto_testbench的大版本升级——加入简单预期与自动比对

前言

前文提要:

【芯片前端】一键生成简易版本定向RTL验证环境的脚本——auto_verification_rtl脚本_尼德兰的喵的博客-CSDN博客

【芯片前端】可能是定向验证的巅峰之作——auto_testbench_autotestbench_尼德兰的喵的博客-CSDN博客

工具路径:

auto…

芯片常见测试手段:CP测试和FT测试

参考链接:

芯片测试的术语解释(FT、CP),持续更新...._ft测试_染不尽的流年的博客-CSDN博客 如何区分芯片cp测试和ft测试 (baidu.com)

芯片常见测试手段:CP测试和FT测试 - 测量仪表 - 电子发烧友网 芯片测试是极其重要…

UVM driver和monitor中阻塞和非阻塞

为什么driver中使用non-blocking赋值,而monitor需要使用blocking赋值? 首先回顾一下 SystemVerilog 的 Scheduler 中的相关概念。

使用 blocking 或者 assign,在Active中更新左值,然后会触发新的评估事件,持续引发事件…

模拟电路基础知识经典 200问,收藏这些就够了!

大家总说模电知识总是学不会,IC修真院为大家整理了模电经典200问,看看你掌握了多少,文末可以获取全部哦。

文末可领全部文档

1、半导体材料制作电子器件与传统的真空电子器件相比有什么特点?

答:频率特性好、体积小、功耗小&…

IC修勾的招聘之路——持续更新中

招聘要求

实习

大疆

实习生(软件开发-GPU/AHPC)

任职要求 能熟练使用 C,了解DSP或NEON代码优化; 了解vector C或intrinsic C编程,掌握cache、DMA等memory优化技能; 加分项:具备GPU/CUDA软…

杂谈:DC对Verilog和SystemVerilog语言的支持

DC对Verilog和SystemVerilog语言的支持 设计语言用哪种?Design Compiler对二者的支持简单的fsm电路测试测试结果对比写在最后 设计语言用哪种?

直接抛出结论:先有电路,后为描述。设计端而言,没有语言的高低好坏&#…

掌握SKILL语言:数字IC设计师必备的技能之一

去年在各个平台更新了一篇《数字IC必学之《Skill入门教程》建议收藏!》,阅读量在每个平台都很客观,且这半年以来,不断有粉丝留言想要获取这份资料。看来大家对于SKILL的需求是很大的,想要掌握SKILL语言:数字…

Verilog Tutorial(10)如何实现可复用的Verilog设计?

本文将讨论可以用来实现代码可复用性的参数parameter和generate语句(生成语句)。与大多数编程语言一样,设计者也应该尽量使verilog代码尽可能地具备可复用性----这能够减少未来项目的开发时间,因为设计者可以更轻松地将代码从一个…

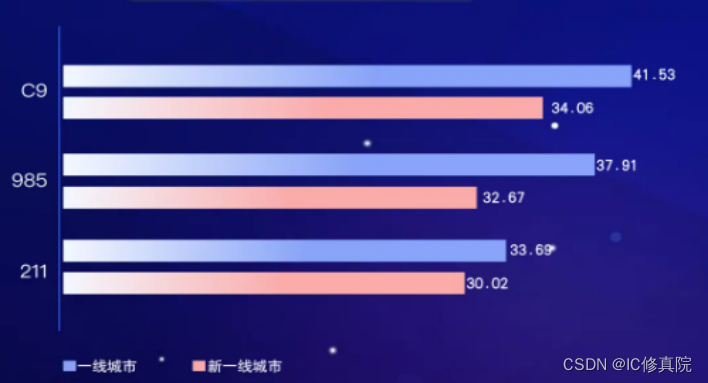

入行IC,优选哪些工作城市?

首先大家要知道大公司的一个布局,他们大都是在北上广深,一般他们都是总部,市场客户支持肯定是要放在这些地方,因为这些地方离客户比较近,ZF也能给予一些优惠政策。

国内优秀的IC设计公司主要分布在以下几个城市:

1.上…

数字IC设计怎么入门?(附学习全流程)

看到很多小伙伴都不了解数字IC设计该怎么学,下面就来给大家来具体讲讲。

其实对于初级数字 IC 设计工程师而言,不仅仅需要较好的 Verilog 语法功底,还要熟悉企业的 Linux 环境以及 EDA 工具,此时你就需要掌握 Shell,V…